Устройство управления

УУ современных процессоров обычно реализуются в виде микропрограммного автомата и в этом случае УУ включает в себя ПЗУ микрокоманд.

УУ предназначено для формирования сигналов управления для всех блоков машины.

В архитектуре фон Неймана является неотъемлемой частью центрального процессора.

Связанные понятия

Разработка синхронных цифровых интегральных схем на уровне передач данных между регистрами (англ. register transfer level, RTL — уровень регистровых передач) — способ разработки синхронных (англ.) цифровых интегральных схем, при применении которого работа схемы описывается в виде последовательностей логических операций, применяемых к цифровым сигналам (данным) при их передаче от одного регистра к другому (не описывается, из каких электронных компонентов или из каких логических вентилей состоит схема.

Упоминания в литературе

Связанные понятия (продолжение)

Ввод-вывод через порты (англ. I/O ports) — схемотехническое решение, организующее взаимодействие процессора и устройств ввода-вывода. Противоположность вводу-выводу через память.

Многоканальный режим (англ. Multi-channel architecture) — режим работы оперативной памяти (RAM) и её взаимодействия с материнской платой, процессором и другими компонентами компьютера, при котором может быть увеличена скорость передачи данных между ними за счёт использования сразу нескольких каналов для доступа к объединённому банку памяти (это можно проиллюстрировать на примере ёмкостей, через горлышко одной из которых жидкость будет выливаться дольше, чем из двух других с такими же общим суммарным.

Mультипле́ксор — устройство, имеющее несколько сигнальных входов, один или более управляющих входов и один выход. Мультиплексор позволяет передавать сигнал с одного из входов на выход; при этом выбор желаемого входа осуществляется подачей соответствующей комбинации управляющих сигналов.

В информатике бу́фер (англ. buffer), мн. ч. бу́феры — это область памяти, используемая для временного хранения данных при вводе или выводе. Обмен данными (ввод и вывод) может происходить как с внешними устройствами, так и с процессами в пределах компьютера. Буферы могут быть реализованы в аппаратном или программном обеспечении, но подавляющее большинство буферов реализуется в программном обеспечении. Буферы используются, когда существует разница между скоростью получения данных и скоростью их обработки.

Латентность (в т.ч. англ. CAS Latency, CL; жарг. тайминг) — временна́я задержка сигнала при работе динамической оперативной памяти со страничной организацией, в частности, SDRAM. Эти временны́е задержки также называют таймингами и для краткости записывают в виде трех чисел, по порядку: CAS Latency, RAS to CAS Delay и RAS Precharge Time. От них в значительной степени зависит пропускная способность участка «процессор-память» и задержки чтения данных из памяти и, как следствие, быстродействие системы.

В информатике и теории автоматов состояние цифровой логической схемы или компьютерной программы является техническим термином для всей хранимой информации, к которой схема или программа в данный момент времени имеет доступ. Вывод данных цифровой схемы или компьютерной программы в любой момент времени полностью определяется его текущими входными данными и его состоянием.

Центральный процессор, системные шины

Дата добавления: 2015-07-04 ; просмотров: 9372 ; Нарушение авторских прав

Процессор выполняет обработку всех видов информации

К основным характеристикам процессора относится тактовая частота

Интерфейс объединения модулей в вычислительную систему, называется общей шиной (или системной магистралью)

Аппаратура сопряжения, позволяющая подключить к процессору другие устройства называется… портом

Основная интерфейсная система компьютера, обеспечивающая сопряжение и связь всех его устройств между собой называется… системной шиной

Устройство управления является составной частью… микропроцессора

Арифметико-логическое устройство (АЛУ) является составной частью… микропроцессора

Микропроцессорная память (МП) является составной частью… микропроцессора

Интерфейсная система является составной частью… микропроцессора

Кодовая шина данных является составной частью… системной шины

Кодовая шина адреса является составной частью… системной шины

Кодовая шина инструкций является составной частью… системной шины

Шина питания является составной частью… системной шины

Запоминающие устройства: классификация, принцип работы, основные характеристики. Системная память: ОЗУ, ПЗУ, кэш. Внешняя память: винчестер; стример; накопитель на гибких магнитных дисках; накопители на компакт-дисках

В состав внутренней памяти современного компьютера НЕ входит… накопители на магнитных дисках

Для временного хранения информации используется оперативная память (ОЗУ)

Невозможно случайно стереть информацию на … CD-R

Устройством для резервного копирования больших объемов информации является стример

дополнительным хранилищем копий блоков информации

Дисковая память является… памятью прямого доступа

КЭШ-память компьютеров: значительно увеличивает емкость оперативной памяти

Устройством, в котором хранение данных возможно только при включенном питании компьютера, является… оперативная память (ОЗУ)

Минимальной адресуемой ячейкой оперативной памяти является байт

Имеет механические части и поэтому работает достаточно медленно ________ память внешняя

Укажите, какие запоминающие устройства из предложенного списка относятся к внутренней памяти: а)жесткие магнитные дискиб) оперативная память в) постоянная память г)гибкие магнитные дискид) кэш-память ( б, в, д)

Укажите, какие устройства из предложенного списка являются устройствами памяти: а) жесткий дискб) джойстик в) мышь г) регистры д) CD-ROM (а, г, д)

Укажите, какие устройства из предложенного списка являются устройствами памяти:а) сканерб) ОЗУв) мышьг) регистры д) CD-ROM (б, г, д)

Внешняя память компьютера предназначена … для долговременного хранения данных и программ

Компакт-диск (CD) – это … оптический диск, информация с которого считывается лазерным лучом

Процедурой исправления ошибок, используемой для защиты данных в памяти компьютера, является … код Хемминга

При отключении компьютера данные не сохраняются … в оперативной памяти (ОЗУ)

Принцип записи данных на гибкий магнитный диск заключается в намагничивании поверхности диска

Устройства ввода/вывода данных, данных, их разновидности и основные характеристики. Клавиатура. Координатные устройства ввода. Видео- и звуковые адаптеры. Назначение, разновидности и основные характеристики. Сканеры. Принтеры. Плоттеры. Мониторы

Модем – это устройство… для связи компьютера с сетью через телефонные линии связи

Разрешение принтера – это число точек, которое различают на линии длиной в один дюйм

Мышь может быть… оптической

Сканер используется для … ввода текстовой и графической информации в компьютер

Джойстик в первую очередь используется как манипулятор в игровых приставках

Выберите устройство ввода мышь

Принтеры классифицируют по типу механизм выполнения печати

НЕ существует мониторов _________ типа лазерного

Устройством ручного ввода графических данных, выполненное в виде рукоятки, связанной с датчиками напряжения, является… джойстик

Не нашли то, что искали? Google вам в помощь!

Устройство управления является составной частью чего

09. Классификация, структуры, функции устройств управления

Устройство управления (УУ) — важнейшая часть ВМ, организующая автоматическое выполнение программ (путем реализации функций управления) и обеспечивающая функционирование ВМ как единой системы. Для пояснения функций УУ ВМ следует рассматривать как совокупность элементов, между которыми происходит пересылка информации, в ходе которой эта информация может подвергаться определенным видам обработки. Пересылка информации между любыми элементами ВМ инициируется своим сигналом управления (СУ), то есть управление вычислительным процессом сводится к выдаче нужного набора СУ в нужной временной последовательности. Основной функцией УУ является формирование управляющих сигналов, отвечающих за извлечение команд из памяти в порядке, определяемом программой, и последующее исполнение этих команд. Кроме того, УУ формирует СУ для синхронизации и координации внутренних и внешних устройств ВМ. Генерируемая управляющим устройством последовательность управляющих сигналов задается поступающими на входы устройства кодом операции, сигналами из операционного блока, несущими информацию об особенностях операндов, промежуточных и конечного результатов операции, а также синхросигналами, задающими границы тактов.

Классифицировать УУ можно по различным признакам: по уровню централизации, по типам длительности тактов в УУ, по реализации хранения алгоритмов микроопераций.

По уровню централизации:

· Централизованные (УУ – один в ВМ)

· Децентрализованные (в каждом блоке – свой УУ)

· Смешанные (1+2 – конвейеров лучше)

По типам длительности тактов:

· Асинхронные. И длительность такта и цикла – переменные. Это обеспечивает самое высокое быстродействие, но возникают сложности в настройке.

· Используют признак завершения операции.

· Группируют микрооперации – по признаку длительности (в каждой группе – свое время выполнения).

Входной информацией для центрального БУ служит код операции текущей команды, который определяет конкретную выполняемую операцию. Он поступает в БУ из регистра команд и служит для выработки сигналов управления, передаваемых на все узлы и устройства компьютера.

Помимо кода операции при работе БУ используются флаги, т. е. признаки, характеризующие результаты выполнения предшествующей операции. Они необходимы для организации выполнения команд условного перехода. Блок управления вырабатывает сигналы при поступлении на него тактовых импульсов. Кроме того, он получает сигналы от системной шины, например запросы прерывания, подтверждения приема информации и т. п.

Блок управления формирует управляющие сигналы, направляемые в различные устройства и блоки компьютера, прежде всего в процессор. Эти сигналы служат для управления перемещением данных между регистрами, работой устройств, инициирования тех или иных функций. Сигналы управления направляются также в шину для передачи в блоки памяти и на устройства ввода-вывода.

Действия в операционном блоке в течение одного такта называются микрооперациями (МО), а любая операция или команда, выполняемая за несколько тактов, описывается некоторой микропрограммой, определяющей последовательность действий при выполнении этой команды. Сигналы управления, формируемые БУ и поступающие на входы операционного устройства, вызывают в нем выполнение микрооперации. Поскольку блоки управления формируют сигналы для выполнения микроопераций, их часто называют микропрограммными автоматами.

В зависимости от способа формирования сигналов управления микрооперациями различают два типа микропрограммных автоматов: с «жесткой» и программируемой логикой.

Устройства управления с «жесткой» логикой. Код операции и номер такта в управляющем автомате с «жесткой» логикой (рис. 5.8) поступают на дешифраторы DC и затем на логические схемы формирования сигналов управления. На эти же схемы, представляющие собой наборы схем совпадения, поступают различные осведомительные сигналы, которые характеризуют результат выполнения: предыдущей операции или микрооперации.

Сигналы для каждой микрооперации в автомате с «жесткой» логикой формируются своим собственным набором логических схем, который невозможно изменить, не меняя всю систему управления компьютером, что и обусловливает название автомата. В состав его схемы входят счетчик и дешифратор тактов, дешифратор кода операции и логические схемы формирования сигналов управления. Время срабатывания этих логических схем мало, поэтому такие аппаратно реализованные микропрограммные автоматы обеспечивают наибольшее быстродействие. Однако их сложность возрастает с расширением системы команд, так как для каждой операции в них должен быть предусмотрен собственный набор схем.

Эти особенности автоматов с «жесткой» логикой привели к тому, что они находят применение в RISC-процессорах, а в компьютерах с расширенной системой команд обычно используют иной подход — микропрограмму, хранимую в специальной памяти.

Второй тип управляющего автомата — автомат с хранимой в памяти логикой. Управление каждой операцией, входящей в систему команд компьютера, осуществляется с помощью хранимых в памяти слов. Эти управляющие слова, или микрокоманды, содержат информацию о микрооперациях, выполняемых в течение одного машинного такта и осуществляющих элементарное преобразование над данными, и указание, где находится следующая микрокоманда. Такое управление получило название микропрограммного.

Микропрограммы для каждой команды компьютера можно разместить в специальной памяти микропрограмм. Таким образом, процесс командного управления становится двухступенчатым: сначала нужно извлечь из основной памяти компьютера команду, а затем для ее выполнения извлечь из памяти микропрограмм последовательность микрокоманд. Для реализации такого двухступенчатого процесса требуется быстрая постоянная память довольно большого объема.

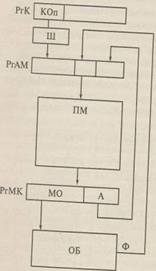

Основное место в типичной структуре устройства управления с хранимой в памяти логикой (рис. 5.9) занимает память микропрограмм (ПМ), в которой находятся все выполняемые микрокоманды. Она является постоянной памятью; адрес очередной микрокоманды (РгАМ) определяется кодом текущей операции (КОп из регистра команд преобразуется шифратором Ш), флагами Ф, полученными при выполнении предыдущей операции (из регистра флагов), и адресной частью предыдущей микрокоманды (А).Очередная МК считывается из памяти и заносится в регистр RG мк, откуда СУ МО поступают в ОБ.

Обобщенная структура управления

В обобщенной структуре УУ (рис. 6.3) можно выделить две части: управляющую и адресную. Управляющая часть УУ предназначена для координирования работы операци онного блока ВМ, адресной части устройства управления, основной памяти и дру гих узлов ВМ. Адресная часть УУ обеспечивает формирование адресов команд и исполнитель ных адресов операндов в основной памяти.

В состав управляющей части УУ входят:

* регистр команды (РК), состоящий из адресной (Адрес) и операционной (КОп, СА) частей; *микропрограммный автомат (МПА); * узел прерываний и приоритетов (УПП)

Регистр команды РК предназначен для приема очередной команды из запоминающего устройства. Микропрограммный автомат на основании результатов расшифровки операционной части команды (КОп, СА) вырабатывает определенную последовательность микрокоманд, вызывающих выполнение всех целевых функций УУ.

Узел прерываний и приоритетов позволяет реагировать на различные ситуации, связанные как с выполнением рабочих программ, так и с состоянием ВМ.

Адресная часть УУ включает в себя:

*операционный узел устройства управления (ОПУУ); *регистр адреса (РгА); *счетчик команд (СК).

Регистр адреса используется для хранения исполнительных адресов операндов, а счетчик команд — для выработки и хранения адресов команд. Содержимое РгА и СК посылается в регистр адреса основной памяти (ОП) для выборки операндов и команд соответственно.

ОПУУ, называемый иначе узлом индексной арифметики или узлом адресной арифметики, обрабатывает адресные части команд, формируя исполнительные адреса операндов, а также подготавливает адрес следующей команды при выпол

28)Устройства управления, структуры, функции

28)Устройства управления, структуры, функции

Устройство управления (УУ) ― важнейшая часть ВМ, организующая автоматическое выполнение программ (путем реализации функций управления) и обеспечивающая функционирование ВМ как единой системы. Для пояснения функций УУ ВМ следует рассматривать как совокупность элементов, между которыми происходит пересылка информации, в ходе которой эта информация может подвергаться определенным видам обработки. Пересылка информации между любыми элементами ВМ инициируется своим сигналом управления (СУ), то есть управление вычислительным процессом сводится к выдаче нужного набора СУ в нужной временной последовательности. Основной функцией УУ является формирование управляющих сигналов, отвечающих за извлечение команд из памяти в порядке, определяемом программой, и последующее исполнение этих команд. Кроме того, УУ формирует СУ для синхронизации и координации внутренних и внешних устройств ВМ.

Описании узлов, реализующих целевую функцию УУ:

Счетчик команд (СК) ― неотъемлемый элемент устройства управления любой ВМ, построенной в соответствии с фон-неймановским принципом программного управления. Согласно этому принципу соседние команды программы располагаются в ячейках памяти со следующими по порядку адресами и выполняются преимущественно в той же очередности, в какой они размещены в памяти ВМ. Таким образом, адрес очередной команды может быть получен путем увеличения адреса ячейки, из которой была считана текущая команда, на длину выполняемой команды, представленную числом занимаемых ею ячеек. Реализацию такого режима и призван обеспечивать счетчик команд ― двоичный счетчик, в котором хранится и модифицируется адрес очередной команды программы. Перед началом вычислений в СК заносится адрес ячейки основной памяти, где хранится команда, которая должна быть выполнена первой. В процессе выполнения каждой команды путем увеличения содержимого СК на длину выполняемой команды в счетчике формируется адрес следующей подлежащей выполнению команды. В рассматриваемой ВМ любая команда занимает одну ячейку, поэтому содержимое СК увеличивается на единицу, что обеспечивается подачей сигнала управления +1СК. По завершении текущей команды адрес следующей команды программы всегда берется из счетчика команд. Для изменения естественного порядка вычислений (перехода в иную точку программы) достаточно занести в СК адрес точки перехода.

Хотя термин «счетчик команд» считается общепринятым, его нельзя признать вполне удачным из-за того, что он создает неверное впечатление о задачах данного узла. По этой причине разработчики ВМ используют иные названия, в частности программный счетчик (PC, Program Counter) или указатель команды (IP, Instruction Pointer). Последнее определение представляется наиболее удачным, поскольку точнее отражает назначение рассматриваемого узла УУ.

В заключение добавим, что в ряде ВМ счетчик команд реализуется в виде обычного регистра, а увеличение его содержимого производится внешней схемой (схемой инкремента/декремента).

Счетчик команд определяет лишь местоположение команды в памяти, но не содержит информации о том, что это за команда. Чтобы приступить к выполнению команды, ее необходимо извлечь из памяти и разместить в регистре команды (РК). Этот этап носит название выборки команды. Только с момента загрузки команды в РК она становится «видимой» для процессора. В РК команда хранится в течение всего времени ее выполнения. Как уже отмечалось ранее, любая команда содержит два поля: поле кода операции и поле адресной части. Учитывая это обстоятельство, регистр команды иногда рассматривают как совокупность двух регистров ― регистра кода операции (РКОп) и регистра адреса (РА), в которых хранятся соответствующие составляющие команды.

Если команда занимает несколько последовательных ячеек, то код операции всегда находится в том слове команды, которое извлекается из памяти первым. Это позволяет по коду операции определить, требуются ли считывание из памяти и загрузка в РК остальных слов команды. Собственно выполнение команды начинается только после занесения в РК ее полного кода.

Указатель стека (УС) ― это регистр, где хранится адрес вершины стека. В реальных вычислительных машинах стек реализуется в виде участка основной памяти, обычно расположенного в области наибольших адресов. Заполнение стека происходит в сторону уменьшения адресов, при этом вершина стека ― это ячейка, куда была произведена последняя по времени запись. Для хранения адреса такой ячейки и предназначен УС.

Регистр адреса памяти

Регистр адреса памяти (РАП) предназначен для хранения адреса ячейки основной памяти вплоть до завершения операции (считывание или запись) с этой ячейкой. Наличие РАП позволяет компенсировать различия в быстродействии ОП и прочих устройств машины.

Регистр данных памяти (РДП) призван компенсировать разницу в быстродействии запоминающих устройств и устройств, выступающих в роли источников и потребителей хранимой информации. В РДП при чтении заносится содержимое ячейки ОП, а при записи ― помещается информация, подлежащая сохранению в ячейке ОП. Собственно момент считывания и записи в ячейку определяется сигналами ЧтЗУ и ЗпЗУ соответственно.

Дешифратор кода операции (ДКОп) преобразует код операции в форму, требуемую для работы микропрограммного автомата (МПА). Информация после декодирования определяет последующие действия МПА, а ее вид зависит от организации МПА. В рассматриваемой ВМ ― это унитарный код УнитК. Часто код операции преобразуется в адрес первой команды микропрограммы, реализующей указанную в команде операцию. С этих позиций ДКОп правильнее было бы назвать не дешифратором, а преобразователем кодов.

Микропрограммный автомат (МПА) правомочно считать центральным узлом устройства управления. Именно МПА формирует последовательность сигналов управления, в соответствии с которыми производятся все действия, необходимые для выборки из памяти и выполнения команд. Исходной информацией для МПА служат: декодированный код операции, состояние признаков (флагов), характеризующих результат предшествующих вычислений, а также внешние запросы на прерывание текущей программы и переход на программу обслуживания прерывания.

Это устройство, как следует из его названия, предназначено для арифметической и логической обработки данных. В машине, изображенной на рис. 3,1, оно содержит следующие узлы.

Операционный блок (ОПБ) представляет собой ту часть АЛУ, которая, собственно, и выполняет арифметические и логические операции над поданными на вход операндами. Выбор конкретной операции из возможного списка операций для данного ОПБ определяется кодом операции команды. В нашей ВМ код операции поступает непосредственно из регистра команды. В реальных машинах КОп зачастую преобразуется в МПА в иную форму и уже из микропрограммного автомата поступает в АЛУ. Операционные блоки современных АЛУ строятся как комбинационные схемы, то есть они не обладают внутренней памятью и до момента сохранения результата операнды должны присутствовать на входе блока.

Регистры РХ и PY обеспечивают сохранение операндов на входе операционного блока вплоть до получения результата операции и его записи (в нашем случае в аккумулятор).

Регистр признаков (РПрз) предназначен для фиксации и хранения признаков (флагов), характеризующих результат последней выполненной арифметической или логической операции. Такие признаки могут информировать о равенстве результата нулю, о знаке результата, о возникновении переноса из старшего разряда, переполнении разрядной сетки и т. д. Содержимое РПрз обычно используется устройством управления для реализации условных переходов по результатам операций АЛУ. Под каждый из возможных признаков отводится один разряд РПрз.

Формирование признаков осуществляется блоком формирования состояний регистра признаков, который может входить в состав ОПБ либо реализуется в виде внешней схемы, располагаемой между операционным блоком и РПрз.

Аккумулятор (Акк) ― это регистр, на который возлагаются самые разнообразные функции. Так, в него предварительно загружается один из операндов, участвующих в арифметической или логической операции. В Акк может храниться результат предыдущей команды и в него же заносится результат очередной операции. Через Акк зачастую производятся операции ввода и вывода.

Строго говоря, аккумулятор в равной мере можно отнести как к АЛУ, так и к У У, а в ВМ с регистровой архитектурой его можно рассматривать как один из регистров общего назначения.

Вне зависимости от типа используемых микросхем основная память (ОП) представляет собой массив запоминающих элементов (ЗЭ), организованных в виде ячеек, способных хранить некую единицу информации, обычно один байт. Каждая ячейка имеет уникальный адрес. Ячейки ОП организованы в виде матрицы» а выбор ячейки осуществляется путем подачи разрешающих сигналов на соответствующие строку и столбец этой матрицы. Это обеспечивается дешифратором адреса памяти, преобразующим поступивший из РАП адрес ячейки в разрешающие

сигналы, подаваемые в горизонтальную и вертикальную линии, на пересечении

которых расположена адресуемая ячейка. При современной емкости ОП для реализации данных сигналов приходится использовать несколько микросхем запоминающих устройств (ЗУ). В этих условиях процесс обращения к ячейке состоит из выбора нужной микросхемы (на основании старших разрядов адреса) и выбора ячейки внутри микросхемы (определяется младшими разрядами адреса). Первая часть процедуры производится внешними схемами, а вторая ― внутри микросхем ЗУ.

Структура приведенного на рис. 3.1 модуля ввода/вывода (МВВ) обеспечивает только пояснение логики работы ВМ. В реальных ВМ реализация этого устройства машины может существенно отличаться от рассматриваемой. Задачей МВВ является обеспечение подключения к ВМ различных периферийных устройств (ПУ) и обмена информацией с ними. В рассматриваемом варианте МВВ состоит из дешифратора номера порта ввода/вывода, множества портов ввода и множества портов вывода.

Порты ввода и порты вывода

Портом называют схему, ответственную за передачу информации из периферийного устройства ввода в аккумулятор АЛУ (порт ввода) или из аккумулятора на периферийное устройство вывода (порт вывода). Схема обеспечивает электрическое и логическое сопряжение ВМ с подключенным к нему периферийным устройством.

Дешифратор номера порта ввода/вывода

В модуле ввода/вывода рассматриваемой ВМ предполагается, что каждое ПУ подключается к своему порту. Каждый порт имеет уникальный номер, который указывается в адресной части команд ввода/вывода. Дешифратор номера порта ввода/ вывода (ДВВ) обеспечивает преобразование номера порта в сигнал, разрешающий операцию ввода или вывода на соответствующем порте. Непосредственно ввод (вывод) происходит при поступлении из МПА сигнала Вв (Выв).

УУ вычислительной машины реализует функции управления ходом вычислительного процесса, обеспечивая автоматическое выполнение команд программы. Процесс выполнения программы в ВМ представляет собой последовательность машинных циклов. Детализируем основные целевые функции, реализуемые устройством управления в ходе типового машинного цикла. Для простоты примем, что ВМ обеспечивает одноадресную систему команд. При этом, в частности, полагается, что до начала выполнения двухоперандной арифметической команды второй операнд уже находится в процессоре.

Первым этапом в машинном цикле является выборка команды из памяти (этап ВК). Целевую функцию этого этапа будем обозначать как ЦФ-ВК.

За выборкой команды следует этап декодирования ее операционной части (кода операции). Для простоты пока будем рассматривать этот этап в качестве состав ной части этапа ВК.

Вторая целевая функция ― формирование адреса следующей команды. На это выделяется специальный такт работы ― этап ФАСК, которому соответствует целевая функция ЦФ-ФАСК.

Далее следует этап формирования исполнительного адреса операнда или адреса перехода (этап ФИА), на котором УУ реализует функцию ЦФ-ФИА. Функция имеет столько модификаций, сколько способов адресации (СА) предусмотрено в системе команд ВМ.

На четвертом этапе реализуется целевая функция выборки операнда (ЦФ-ВО) из памяти по исполнительному адресу, сформированному на предыдущем этапе.

Наконец, на последнем этапе машинного цикла действия задаются целевой функцией исполнения операции ― ЦФ-ИО. Очевидно, что количество модификаций ЦФ-ИО равно количеству операций, имеющихся в системе команд ВМ.

Модель устройства управления

— флаги — требуются устройству управления для оценки состояния ЦП и результата предшествующей операции, что необходимо при выполнении команд условного перехода;

— сигналы из системной шины — часть сигналов с системной шины, обеспечивающая передачу в УУ запросов прерывания, подтверждений и т. п. В свою очередь, УУ, а точнее микропрограммный автомат, формирует следующую выходную информацию:

— внутренние сигналы управления — эти сигналы воздействуют на внутренние схемы центрального процессора и относятся к одному из двух типов: тем, которые вызывают перемещение данных из регистра в регистр, и тем, что инициируют определенные функции операционного устройства ВМ;

— сигналы в системную шину — также относятся к одному из двух типов: управля ющие сигналы в память и управляющие сигналы в модули ввода/вывода.

Структура устройства управления

Как уже отмечалось ранее, процесс функционирования ВМ состоит из последовательности элементарных действий в ее узлах. Такие элементарные преобразования информации, выполняемые в течение одного такта сигналов синхронизации, называются микрооперациями (МО). Совокупность сигналов управления, вызывающих одновременно выполняемые микрооперации, образует микрокоманду (МК). В свою очередь, последовательность микрокоманд, определяющую содержание и порядок реализации машинного цикла, принято называть микропрограммой. Сигналы управления вырабатываются устройством управления, а точнее одним из его узлов — микропрограммным автоматом (МПА). Название отражает то, что МПА определяет микропрограмму как последовательность выполнения микроопераций.

Микропрограммы реализации перечисленных ранее целевых функций инициируются задающим оборудованием, которое вырабатывает требуемую последовательность сигналов управления и входит в состав управляющей части УУ.

Выполняются микропрограммы исполнительным оборудованием, входящим в состав основной памяти (для ЦФ-ВК и ЦФ-ВО) и операционного устройства (для ЦФ-ИО). Исполнительным оборудованием для целевых функций ЦФ-ФАСК, ЦФ-ФИА служит адресная часть устройства управления. В обобщенной структуре УУ (рис. 6.3) можно выделить две части: управляющую и адресную.

Управляющая часть УУ предназначена для координирования работы операционного блока ВМ, адресной части устройства управления, основной памяти и других узлов ВМ.

Адресная часть УУ обеспечивает формирование адресов команд и исполнительных адресов операндов в основной памяти. В состав управляющей части УУ входят:

— регистр команды (РК), состоящий из адресной (Адрес) и операционной (КОп, СА) частей;

— микропрограммный автомат (МПА);

— узел прерываний и приоритетов УПП).

Регистр команды РК предназначен для приема очередной команды из запоминающего устройства. Микропрограммный автомат на основании результатов расшифровки операционной части команды (КОп, СА) вырабатывает определенную последовательность микрокоманд, вызывающих выполнение всех целевых функций УУ.

В зависимости от способа формирования микрокоманд различают микропрограммные автоматы:

— с жесткой или аппаратной логикой;

— с программируемой логикой.

Организация МПА этих двух типов будет рассмотрена в последующих разделах.

Узел прерываний и приоритетов позволяет реагировать на различные ситуации, связанные как с выполнением рабочих программ, так и с состоянием ВМ.

Адресная часть УУ включает в себя:

– операционный узел устройства управления (ОПУУ);

– регистр адреса (РгА);

Регистр адреса используется для хранения исполнительных адресов операндов, а счетчик команд — для выработки и хранения адресов команд. Содержимое РгА и СК посылается в регистр адреса основной памяти (ОП) для выборки операндов и команд соответственно.

ОПУУ, называемый иначе узлом индексной арифметики или узлом адресной арифметики, обрабатывает адресные части команд, формируя исполнительные адреса операндов, а также подготавливает адрес следующей команды при выполнении команд перехода. Состав ОПУУ может быть аналогичен составу основного операционного устройства ВМ (иногда в простейших ВМ с целью экономии затрат на оборудование ОПУУ совмещается с основным операционным устройством).

Сказанное об адресной части УУ проиллюстрируем примерами. Пусть в ОПУУ входят два индексных регистра ИР,, ИР2 и индексный сумматор СМИ, как показано на рис. 6.4.

Для данной схемы микропрограмма формирования исполнительного адреса имеет вид, представленный на рис. 6.5, а.

управляющему сигналу BjMPj (B^Pj) индекс адреса из HPt (ИРг) подается на левый вход сумматора СМИ. Одновременно по управляющему сигналу В^К на правый вход СМИ поступает адресная часть команды из регистра команды — РК(а). Осуществляется микрооперация сложения, результат которой (Аисп) по управляющему сигналу П2РгА заносится в РгА. Если СА = 3, то адрес формируется по способу прямой адресации. В этом случае по управляющему сигналу В, РК выполняется микрооперация сложения адресной части РК с нулем. Результат сложения по управляющему сигналу П2РгА с выхода СМИ записывается в РгА.

Микропрограмма формирования адреса следующей команды (ЦФ-ФАСК) изображена на рис. 6.5, б. Видим, что естественное формирование адреса следующей команды (с помощью СК) не производится, если исполняется команда безусловного (БП) или условного (УП) перехода. Такой адрес формируется на этапах ФИА и ИО, он равен исполнительному адресу (если это УП и условие перехода выполняется, или если это БП).

В состав УУ могут также входить дополнительные узлы, в частности узел организации прямого доступа к памяти. Этот узел обычно реализуется в виде самостоятельного устройства — контроллера прямого доступа к памяти (КПДП). КПДП обеспечивает совмещение во времени работы операционного устройства с процессом обмена информацией между ОП и другими устройствами ВМ, тем самым повышая общую производительность машины.

Довольно часто регистры различных узлов УУ объединяют в отдельный узел управляющих (специальных) регистров устройства управления.

Рис. 6.5. Микропрограмма формирования: а — исполнительного адреса; б — адреса

29)МПА с жесткой логикой. Пример синтеза.

Микропрограммный автомат с жесткой логикой

Обычно тип микропрограммного автомата (МПА), формирующего сигналы управления, определяет название всего УУ. Так, УУ с жесткой логикой управления имеет в своем составе МПА с жесткой (аппаратной) логикой. При создании такого МПА выходные сигналы управления реализуются за счет однажды соединенных между собой логических схем.

Типичная структура микропрограммного автомата с жесткой логикой управления показана на рис. 6.6.

Исходной информацией для УУ (см. рис. 6.2) служат: содержимое регистра команды, флаги, тактовые импульсы и сигналы, поступающие с шины управления.

Код операции, хранящийся в РК, используется для определения того, какие СУ и в какой последовательности должны формироваться, при этом, с целью упрощения логики управления, желательно иметь в УУ отдельный логический сигнал для каждого кода операции. Это может быть реализовано с помощью дешифратора. Дешифратор кода операции преобразует код j-й операции, поступающей из регистра команды (РК), в единичный сигнал на j-м выходе.

Машинный цикл выполнения любой команды состоит из нескольких тактов. Сигналы управления, по которым выполняется каждая микрооперация, должны вырабатываться в строго определенные моменты времени, поэтому все СУ «привязаны» к импульсам синхронизации (СИ), формируемым узлом синхроимпульсов. Период СИ должен быть достаточным для того, чтобы сигналы успели распространиться по трактам данных и другим цепям. Каждый СУ ассоциируется с одним из тактовых периодов в рамках машинного цикла. Формирование сигналов, отмечающих начало очередного тактового периода, возлагается на инхронизатор. Синхронизатор содержит счетчик тактов, осуществляющий подсчет СИ. Узел синхроимпульсов после завершения очередного такта работы добавляет к содержимому счетчика тактов единицу. К выходам счетчика подключен дешифратор тактов, с которого и снимаются сигналы тактовых периодов T. В i-м состоянии счетчика тактов, то есть во время i-ro такта, дешифратор тактов вырабатывает единичный сигнал на своем i-м выходе. При такой организации в УУ должна быть предусмотрена обратная связь, с помощью которой по окончании цикла команды счетчик тактов опять устанавливается в состояние T1. Дополнительным фактором, влияющим на последовательность формирования СУ, являются состояние осведомительных сигналов (флагов), отражающих ход вычислений, и сигналы с шины управления. Эта информация также поступает на вход УУ, причем каждая линия здесь рассматривается независимо от остальных.

Процесс синтеза схемы МПА с жесткой логикой называется структурным синтезом и разделяется на следующие этапы:

— выбор типа логических и запоминающих элементов;

— кодирование состояний автомата;

— синтез комбинационной схемы, формирующей выходные сигналы.

Принцип построения логических схем формирования управляющих сигналов поясняется на рис. 6.7. Здесь показан фрагмент схемы, обеспечивающей выработку управляющего сигнала Ск в г-м и 5-м тактах выполнения команды с кодом операции j, причем сигнал Ск появляется в i—м такте только при значениях осведомительных сигналов x1=3, x3=11,а в S-м такте всегда.

Таким образом, название «жесткая логика» обусловлено тем, что каждой микропрограмме здесь соответствует свой набор логических схем с фиксированными связями между ними. При реализации простой системы команд узлы МПА с жесткой логикой экономичны и позволяют обеспечить наибольшее быстродействие из всех возможных методов построения МПА. Однако с возрастанием сложности системы команд соответственно усложняются и схемы автоматов с жесткой логикой, в результате чего уменьшается их быстродействие. Второй недостаток МПА с жесткой логикой — малая регулярность, а следовательно, и большие трудности при размещении УУ такого типа на кристалле интегральной микросхемы.

30)МПА с программируемой логикой. Пример синтеза.

Микропрограммный автомат с программируемой логикой

Идея заинтересовала многих конструкторов ВМ, но была нереализуема, поскольку требовала использования быстрой памяти относительно большой емкости. Вновь вернулись к ней в 1964 году, в ходе создания системы IBM 360. С тех пор устройства управления с программируемой логикой стали чрезвычайно популярными и были встроены во многие ВМ. В этой связи следует упомянуть запатентованный академиком принцип ступенчатого микропрограммирования, который он впервые реализовал в машине «Проминь».