Применение микросхем загрузочного ППЗУ 5576РС1У(РТ1У) для конфигурирования ПЛИС Intel Altera, Xilinx, ВЗПП-С (5576ХСх)

При использовании микросхемы памяти для конфигурации FPGA компании Миландр, в первую очередь при работе необходимо учитывать следующие аспекты:

1. Модель используемой микросхемы ПЛИС. Производитель гарантирует работу со следующими семействами популярных микросхем ПЛИС:

Представленные рекомендации не ограничиваются лишь этими семействами и могут быть распространены на микросхемы других семейств в случае совместимости. Необходимо руководствоваться логикой работы микросхемы памяти и временными диаграммами для последовательного интерфейса конфигурирования согласно официальной поставляемой документации. Ключевое решение принимает разработчик аппаратуры.

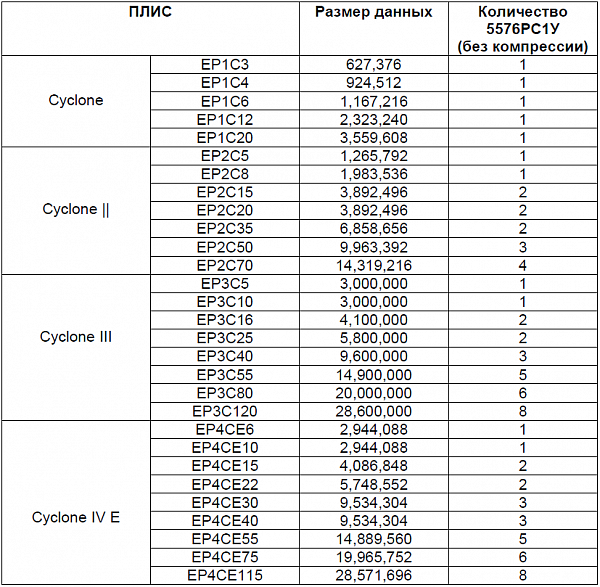

2. В зависимости от размера данных, необходимого для конфигурации той или иной микросхемы ПЛИС, важно связать каскадным образом нужное количество микросхем памяти, учитывая вдобавок и объем памяти микросхем 5576РС1У(РТ1У).

Например, если в изделии используется ПЛИС от Intel Altera семейства Cyclone IV EP4CE22, то на основании информации о том, что размер конфигурационных данных для данной микросхемы равен 5.748.552 бит, потребуется использовать две микросхемы 5576РС1У.

Важно отметить, что программными средствами (подробнее ниже) можно выбрать режим компрессии (уменьшение размера файла при сохранении исходных данных) конфигурационных данных, из-за чего конфигурационный образ будет занимать меньше места. Но следует учитывать, что ППЗУ 576РС1У не содержит схему декодирования сжатых данных, поэтому эту опцию можно применять лишь для тех ПЛИС, которые в своём составе содержат схему декодирования и не требуют предварительного раскодирования данных. Представленная в примере ПЛИС Cyclone IV содержит в своём составе такую схему, поэтому для неё можно использовать компрессию, и такое применение позволит использовать меньше микросхем памяти, соответственно, позволит отказаться от каскадного соединения микросхем.

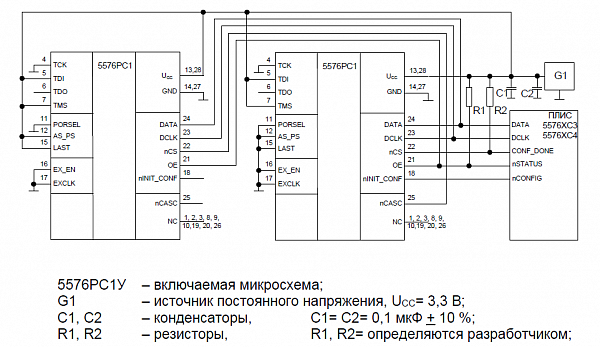

Метод каскадного объединения двух микросхем памяти представлен типовой схемой включения 5576РС1У из официальной документации, наглядно на рисунке 1.

Каскадным образом можно объединить не только две микросхемы памяти, но и гораздо больше. Необходимо учитывать особенности конкретной микросхемы ПЛИС, ровно как и особенности подключения ПЛИС к конфигурационному устройству согласно документации. В свою очередь следует выделить следующие особенности для каскадного объединения микросхем памяти:

3. На основании пункта 2, если применяется каскадное включение микросхем памяти на плате, необходимо при разработке учитывать расположение микросхем памяти друг относительно друга и относительно микросхемы ПЛИС. Это необходимо для минимизации длин цепей DATA и DCLK.

Например, если каскадным образом включены две микросхемы памяти (учитывать длины линий необходимо и при одной микросхеме памяти для конфигурации ПЛИС аналогичным способом), то:

Соответственно, чем больше длины этих цепей или разница в длине от источника к разным приёмникам, тем больше вероятность возникновения ошибок при конфигурировании.

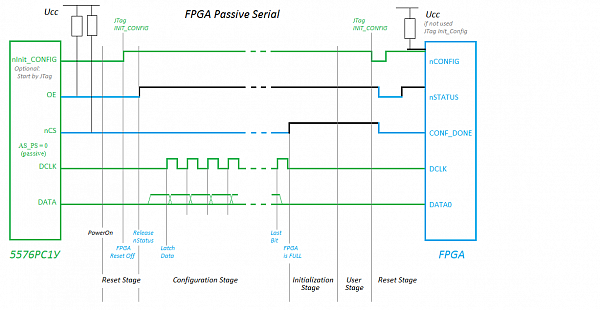

4. Пассивный режим конфигурации. Прежде чем перейти к описанию особенностей работы в этом режиме, рассмотрим, что он из себя представляет. В этом режиме синхросигнал для обмена данными формируется на выводе DCLK микросхемы памяти, этот сигнал является входным для ПЛИС. Режим данный выбирается при логическом нуле на выводе AS_PS микросхемы памяти, поэтому его применение должно закладываться на этапе проектирования изделия. Диаграмма конфигурации в этом режиме представлена на рисунке 2.

В качестве теории опишем процесс конфигурирования данной организации подключения в несколько шагов:

стадия инициализации. После получения данных в FPGA проходит инициализация, то есть применяется настройка пользователя. Выводы User IO переключаются в заданный режим;

При использовании же активного режима конфигурации (AS_PS = 1), синхросигнал формируется на выводе DCLK ПЛИС и является входным для конфигурационного устройства (микросхемы памяти). Подход к созданию файла конфигурации в этом случае стандартный и будет описан ниже (отдельные действия по настройке сигналов для корректного выхода ПЛИС в пользовательский режим в процессе создания бинарного файла выполнять в этом режиме не нужно).

5. Особенность работы чистой микросхемы памяти 5576РС1У и ПЛИС.

Зачастую в ходе разработки проекта необходимо подключаться к ПЛИС через её отладочный интерфейс при помощи программатора. В случае работы с микросхемой памяти 5576РС1У необходимо учитывать, что если она уже подключена напрямую к ПЛИС и является полностью пустой, то на её вывод nINIT_CONF выдаётся постоянный логический ноль, что может делать недоступным отладочный интерфейс ПЛИС. Таким образом ключевых решений два:

Как ранее упоминалось, необходимо учитывать размер данных конфигурации для конкретной ПЛИС, и на основе этого подключать каскадным образом нужное количество микросхем памяти. Более наглядно для микросхем ПЛИС семейства Cyclone информация представлена на рисунке 3.

Размер данных, необходимый для конфигурации других микросхем ПЛИС, должен быть представлен в официальной документации.

На самом же деле Миландр всегда рекомендует прибегать к созданию файлов .pof посредством официально поставляемых программ, поскольку в сложных схемах подключения автоматически созданный файл .pof средствами САПР может приводить к некорректному конфигурированию ПЛИС, что будет сопровождаться либо запуском с ошибками, либо отсутствием запуска вовсе.

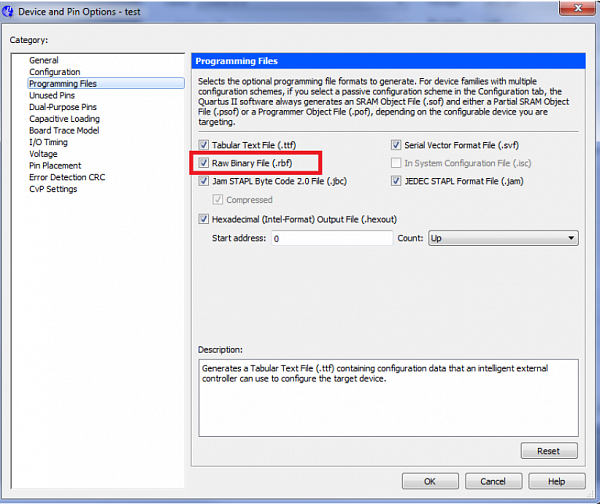

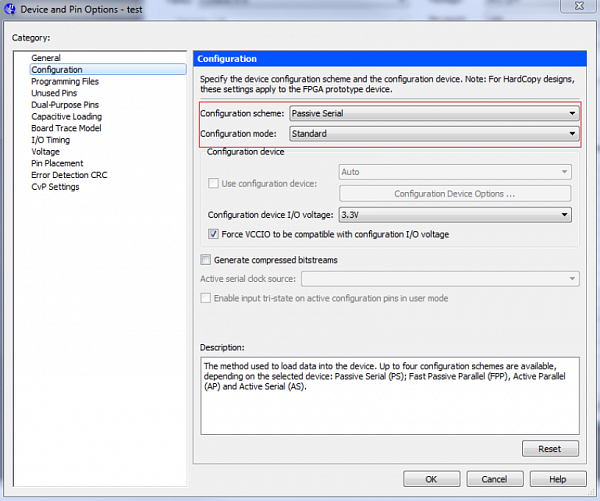

В случае с рассматриваемыми семействами ПЛИС компании Intel Altera работа будет вестись в САПР Quartus II. Всё начинается с создания бинарного файла .rbf. Для его создания на закладке, представленной на рисунке 4, необходимо установить флажок в строке «Raw Binary File (.rbf)»

Аналогично данным для семейства ПЛИС Cyclone, приведем на рисунке 6 размер данных конфигурации, требуемый для ПЛИС семейств Spartan 3 и Spartan 6, а также необходимое количество микросхем памяти 5576РС1У.

Размер данных, необходимый для конфигурации других микросхем ПЛИС, должен быть представлен в официальной документации.

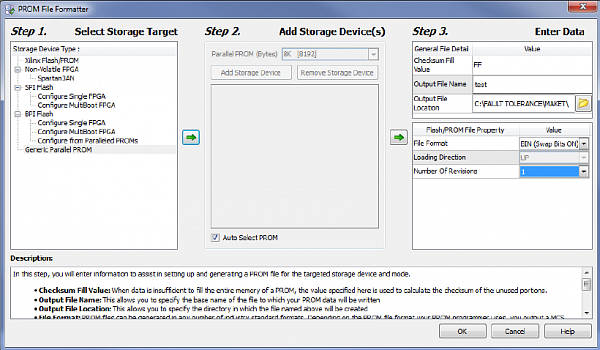

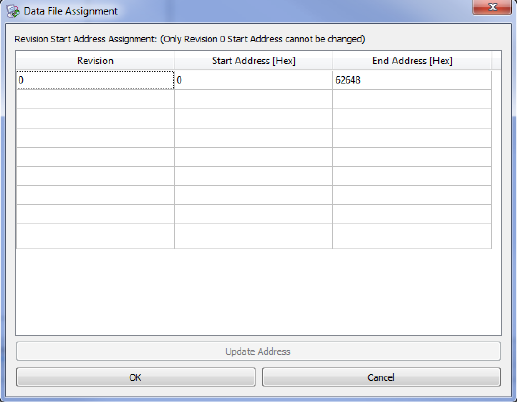

То есть, выбрав задачу «Create PROM File» в подпрограмме iMPACT среды ISE, на шаге 1 необходимо выбрать пункт «Generic Parallel PROM», на шаге 2 установить флажок «Auto Select PROM», на шаге 3 выбрать формат выходного файла «BIN (Swap Bits ON)», имя выходного файла и директорию, в которой он будет располагаться. После этого нажать «ОК», В следующем окне «Add Device» опять следует нажать «ОК» и выбрать файл формата .bit, который был создан при компиляции Вашего проекта в САПР ISE. На предложение добавить еще одно устройство ответить «No» и в следующем сообщении об окончании добавления устройства нажать «ОК». В результате всех выполненных действий должно появится окно, представленное на рисунке 8.

Здесь необходимо нажать «ОК» и после этого сгенерировать файл с помощью «Generate File». После этого будет создан файл с расширением .bin в ранее указанной директории.

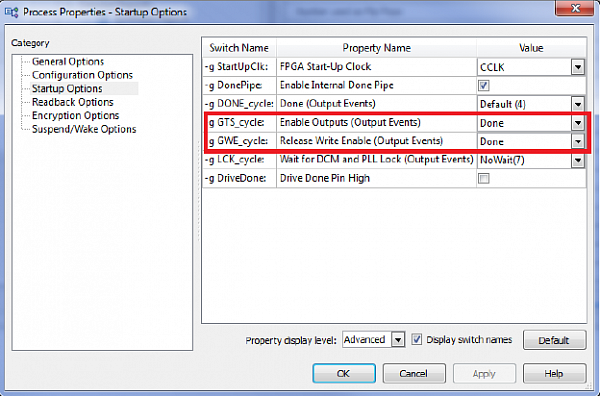

Важно отметить, что при работе в пассивном режиме конфигурации также необходимо обеспечить достаточно большое количество тактов для перехода ПЛИС в пользовательский режим, которое микросхема памяти не может обеспечить. Для обеспечения этого условия на закладке САПР ISE, представленной на рисунке 9, требуется установить соответствующие опции.

После установки этих опций нужно заново создать файл .bit в процессе перекомпиляции проекта, а затем и .bin файл согласно инструкциям, описанным выше. Соответственно, для активного режима конфигурации данная настройка не требуется.

Первая программа из этой группы «rbf2svf.exe», которая конвертирует полученный на этапе компиляции бинарный файл в формат .svf.

Синтаксис этой программы следующий:

После создания файла формата .svf, этот файл передается другой программе «svf2pof.exe». Эта программа разработана компанией Altera и её можно найти на их официальном сайте с оригинальным названием «convert_epc_file.exe». Для понимания производимых процедурой действий она была переименована.

Синтаксис этой программы следующий:

Синтаксис в этом случае следующий:

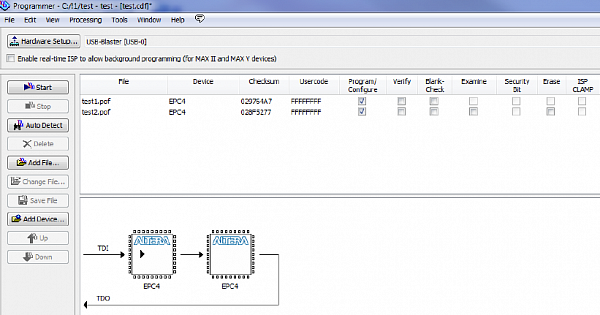

После полученных файлов .pof можно приступать к их загрузке в соответствующие ППЗУ с помощью САПР Quartus II, подпрограмма «Programmer» средствами USB Blaster.

Если же требуется каскадное включение более двух микросхем ППЗУ, то следует учитывать следующие особенности работы программы «rbf2svf.exe». Разбиение на файлы ориентировано на чётное количество байт в бинарном файле (при разбиении на соответствующее количество ППЗУ) и на чётное количество ППЗУ в цепочке. Если требуется загрузка нечётного количества байт или количество ППЗУ в цепочке нечётное, то требуется доработка «rbf2svf.exe» под конкретное приложение. Для решения этой задачи в архиве PROM_CREATOR.zip приложены исходные коды этой программы.

Задача выполнена. Конфигурация для ПЛИС готова.

Сохранить статью в PDF

Применение микросхем загрузочного ППЗУ 5576РС1У(РТ1У) для конфигурирования ПЛИС Intel Altera, Xilinx, ВЗПП-С (5576ХСх)

При использовании микросхемы памяти для конфигурации FPGA компании Миландр, в первую очередь при работе необходимо учитывать следующие аспекты:

1. Модель используемой микросхемы ПЛИС. Производитель гарантирует работу со следующими семействами популярных микросхем ПЛИС:

Представленные рекомендации не ограничиваются лишь этими семействами и могут быть распространены на микросхемы других семейств в случае совместимости. Необходимо руководствоваться логикой работы микросхемы памяти и временными диаграммами для последовательного интерфейса конфигурирования согласно официальной поставляемой документации. Ключевое решение принимает разработчик аппаратуры.

2. В зависимости от размера данных, необходимого для конфигурации той или иной микросхемы ПЛИС, важно связать каскадным образом нужное количество микросхем памяти, учитывая вдобавок и объем памяти микросхем 5576РС1У(РТ1У).

Например, если в изделии используется ПЛИС от Intel Altera семейства Cyclone IV EP4CE22, то на основании информации о том, что размер конфигурационных данных для данной микросхемы равен 5.748.552 бит, потребуется использовать две микросхемы 5576РС1У.

Важно отметить, что программными средствами (подробнее ниже) можно выбрать режим компрессии (уменьшение размера файла при сохранении исходных данных) конфигурационных данных, из-за чего конфигурационный образ будет занимать меньше места. Но следует учитывать, что ППЗУ 576РС1У не содержит схему декодирования сжатых данных, поэтому эту опцию можно применять лишь для тех ПЛИС, которые в своём составе содержат схему декодирования и не требуют предварительного раскодирования данных. Представленная в примере ПЛИС Cyclone IV содержит в своём составе такую схему, поэтому для неё можно использовать компрессию, и такое применение позволит использовать меньше микросхем памяти, соответственно, позволит отказаться от каскадного соединения микросхем.

Метод каскадного объединения двух микросхем памяти представлен типовой схемой включения 5576РС1У из официальной документации, наглядно на рисунке 1.

Каскадным образом можно объединить не только две микросхемы памяти, но и гораздо больше. Необходимо учитывать особенности конкретной микросхемы ПЛИС, ровно как и особенности подключения ПЛИС к конфигурационному устройству согласно документации. В свою очередь следует выделить следующие особенности для каскадного объединения микросхем памяти:

3. На основании пункта 2, если применяется каскадное включение микросхем памяти на плате, необходимо при разработке учитывать расположение микросхем памяти друг относительно друга и относительно микросхемы ПЛИС. Это необходимо для минимизации длин цепей DATA и DCLK.

Например, если каскадным образом включены две микросхемы памяти (учитывать длины линий необходимо и при одной микросхеме памяти для конфигурации ПЛИС аналогичным способом), то:

Соответственно, чем больше длины этих цепей или разница в длине от источника к разным приёмникам, тем больше вероятность возникновения ошибок при конфигурировании.

4. Пассивный режим конфигурации. Прежде чем перейти к описанию особенностей работы в этом режиме, рассмотрим, что он из себя представляет. В этом режиме синхросигнал для обмена данными формируется на выводе DCLK микросхемы памяти, этот сигнал является входным для ПЛИС. Режим данный выбирается при логическом нуле на выводе AS_PS микросхемы памяти, поэтому его применение должно закладываться на этапе проектирования изделия. Диаграмма конфигурации в этом режиме представлена на рисунке 2.

В качестве теории опишем процесс конфигурирования данной организации подключения в несколько шагов:

стадия инициализации. После получения данных в FPGA проходит инициализация, то есть применяется настройка пользователя. Выводы User IO переключаются в заданный режим;

При использовании же активного режима конфигурации (AS_PS = 1), синхросигнал формируется на выводе DCLK ПЛИС и является входным для конфигурационного устройства (микросхемы памяти). Подход к созданию файла конфигурации в этом случае стандартный и будет описан ниже (отдельные действия по настройке сигналов для корректного выхода ПЛИС в пользовательский режим в процессе создания бинарного файла выполнять в этом режиме не нужно).

5. Особенность работы чистой микросхемы памяти 5576РС1У и ПЛИС.

Зачастую в ходе разработки проекта необходимо подключаться к ПЛИС через её отладочный интерфейс при помощи программатора. В случае работы с микросхемой памяти 5576РС1У необходимо учитывать, что если она уже подключена напрямую к ПЛИС и является полностью пустой, то на её вывод nINIT_CONF выдаётся постоянный логический ноль, что может делать недоступным отладочный интерфейс ПЛИС. Таким образом ключевых решений два:

Как ранее упоминалось, необходимо учитывать размер данных конфигурации для конкретной ПЛИС, и на основе этого подключать каскадным образом нужное количество микросхем памяти. Более наглядно для микросхем ПЛИС семейства Cyclone информация представлена на рисунке 3.

Размер данных, необходимый для конфигурации других микросхем ПЛИС, должен быть представлен в официальной документации.

На самом же деле Миландр всегда рекомендует прибегать к созданию файлов .pof посредством официально поставляемых программ, поскольку в сложных схемах подключения автоматически созданный файл .pof средствами САПР может приводить к некорректному конфигурированию ПЛИС, что будет сопровождаться либо запуском с ошибками, либо отсутствием запуска вовсе.

В случае с рассматриваемыми семействами ПЛИС компании Intel Altera работа будет вестись в САПР Quartus II. Всё начинается с создания бинарного файла .rbf. Для его создания на закладке, представленной на рисунке 4, необходимо установить флажок в строке «Raw Binary File (.rbf)»

Аналогично данным для семейства ПЛИС Cyclone, приведем на рисунке 6 размер данных конфигурации, требуемый для ПЛИС семейств Spartan 3 и Spartan 6, а также необходимое количество микросхем памяти 5576РС1У.

Размер данных, необходимый для конфигурации других микросхем ПЛИС, должен быть представлен в официальной документации.

То есть, выбрав задачу «Create PROM File» в подпрограмме iMPACT среды ISE, на шаге 1 необходимо выбрать пункт «Generic Parallel PROM», на шаге 2 установить флажок «Auto Select PROM», на шаге 3 выбрать формат выходного файла «BIN (Swap Bits ON)», имя выходного файла и директорию, в которой он будет располагаться. После этого нажать «ОК», В следующем окне «Add Device» опять следует нажать «ОК» и выбрать файл формата .bit, который был создан при компиляции Вашего проекта в САПР ISE. На предложение добавить еще одно устройство ответить «No» и в следующем сообщении об окончании добавления устройства нажать «ОК». В результате всех выполненных действий должно появится окно, представленное на рисунке 8.

Здесь необходимо нажать «ОК» и после этого сгенерировать файл с помощью «Generate File». После этого будет создан файл с расширением .bin в ранее указанной директории.

Важно отметить, что при работе в пассивном режиме конфигурации также необходимо обеспечить достаточно большое количество тактов для перехода ПЛИС в пользовательский режим, которое микросхема памяти не может обеспечить. Для обеспечения этого условия на закладке САПР ISE, представленной на рисунке 9, требуется установить соответствующие опции.

После установки этих опций нужно заново создать файл .bit в процессе перекомпиляции проекта, а затем и .bin файл согласно инструкциям, описанным выше. Соответственно, для активного режима конфигурации данная настройка не требуется.

Первая программа из этой группы «rbf2svf.exe», которая конвертирует полученный на этапе компиляции бинарный файл в формат .svf.

Синтаксис этой программы следующий:

После создания файла формата .svf, этот файл передается другой программе «svf2pof.exe». Эта программа разработана компанией Altera и её можно найти на их официальном сайте с оригинальным названием «convert_epc_file.exe». Для понимания производимых процедурой действий она была переименована.

Синтаксис этой программы следующий:

Синтаксис в этом случае следующий:

После полученных файлов .pof можно приступать к их загрузке в соответствующие ППЗУ с помощью САПР Quartus II, подпрограмма «Programmer» средствами USB Blaster.

Если же требуется каскадное включение более двух микросхем ППЗУ, то следует учитывать следующие особенности работы программы «rbf2svf.exe». Разбиение на файлы ориентировано на чётное количество байт в бинарном файле (при разбиении на соответствующее количество ППЗУ) и на чётное количество ППЗУ в цепочке. Если требуется загрузка нечётного количества байт или количество ППЗУ в цепочке нечётное, то требуется доработка «rbf2svf.exe» под конкретное приложение. Для решения этой задачи в архиве PROM_CREATOR.zip приложены исходные коды этой программы.

Задача выполнена. Конфигурация для ПЛИС готова.

Сохранить статью в PDF

Какое назначение имеет вывод oe

_________________

«Еще я хотел бы, чтобы наши ученые изобрели какой-то новый источник энергии, чтобы мы на коленях не ползали даже перед нашими братьями, умоляя их и выпрашивая тонну нефти или кубометр газа», — рассказал белорусский президент.

Зарегистрируйтесь и получите два купона по 5$ каждый:https://jlcpcb.com/cwc

Koshelev  | | ||

Зарегистрирован: Сб июн 12, 2010 20:15:29 |

| ||

| |||

Koshelev  | | ||

Зарегистрирован: Сб июн 12, 2010 20:15:29 |

| ||

| |||

| Страница 1 из 1 | [ Сообщений: 4 ] |

Часовой пояс: UTC + 3 часа

Кто сейчас на форуме

Сейчас этот форум просматривают: нет зарегистрированных пользователей и гости: 103